扫描关注 乐鱼体育直播

TI案例:新一代电源模块更快速的瞬时响应方法

时间: 2024-06-27 03:09:24 | 作者: 乐鱼体育网址板,如高阶通信系统,设计人员愈来愈需要为不同的DSP、FPGA、ASIC和微处理器提供更多的瞬时的情况下,将电压偏差降到最低。越来越要关注的问题是,在使用先进IC时,如最新的GHz级DSP、FPGA、ASIC和微处理器,电流瞬时期间会出现输出电压的峰值偏差。如果核心电压(VCC)超出指定的容差上限,IC必须重设,否则会发生逻辑错误。为避免发生这种状况,设计人需要更注意所使用的负载点(point-of-load, POL)模块瞬时效能。

最新GHz级DSP之类的数字负载需要相当快速的瞬时响应,以及相当低的电压偏差。为达到这些目标,常常要为DC/DC转换器加装多个输出电容,让它在回馈回路响应前有足够的维持时间。使用电源模块,并加装电容以符合电压瞬时容差后,便形成一套完整的电源解决方案。

由于设计人员逐渐增加输出电容,因此瞬时幅度会降低,然而,增加电容会降低电源系统频宽,高电能储存的优点会被缓慢的响应时间抵消。

借由创新的DC/DC电源模块技术,系统模块设计人员如今可以应用较少的输出电容,达到更快速的瞬时响应及更低的电压偏差。德州仪器的T2系列新一代PTH模块(见图1)便是其中一例,这个系列的模块结合一项全新的TurboTrans技术,能够大幅度减少客户为达到特定电压偏差目标而使用输出电容的需求。这项专利技术的运作方式是修改模块的控制回路,让设计人员自行调整模块,以符合特定的瞬时负载需求,只需增加一个外部电阻就能够实现调整工作。

在高瞬时负载的应用中,TurboTrans技术能够让设计人员减少高达8倍数量的输出电容,同时将电压偏差降低,因此能节约电容成本与印刷电路板空间。这项技术的另一项优点是提升超低ESR电容的稳定性。设计人员便可使用较新的Oscon输出电容、聚合物钽质输出电容或所有陶瓷输出电容,而完全不需顾虑稳定性问题。如此一来,便可以应用可达到高温无铅焊锡规范的电容技术。

TurboTrans技术能够减少增加电容以达到特定瞬时目标的需求。对于TI的额定30A PTH08T210W之类的模块,经证实可减少高达8倍数量的电容。图2显示改变量为5A/μs的10A负载步阶所需的50mV最大偏差瞬时目标范例。第一张图显示 PTH08T210W以470μF的最低需求输出电容运作,而且TurboTrans功能已关闭。电压偏差由于瞬时而达到150mV。为满足所需的50mV偏差值,设计人员总共需要10 560μF的输出电容,如第二张图所示,这是未使用Turbo Trans功能的模块常见的结果。第三张图则显示使用TurboTrans功能的结果,其中只需要1320μF的输出电容。

这个范例显示减少的电容有8倍之多。当然,减少所需的电容与使用的电容类型有关,因每个电容类型都有各自的寄生阻抗。不同的电容类型有不同的ESR与ESL特性,低ESR电容贮电模块相当适合采用TurboTrans技术。

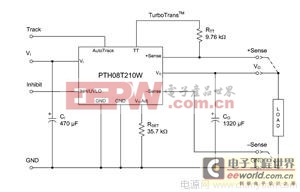

透过先进的TurboTrans技术,系统模块设计人员如今能够在较短的设计过程中以极低的成本使用POL模块,以达到特定的瞬时负载需求。如图3所示,这只需要在T2系列模块的VSENSE接脚与TurboTrans接脚之间接上电阻,从而就可依据数据表决定电阻的值与所需的电容数量。

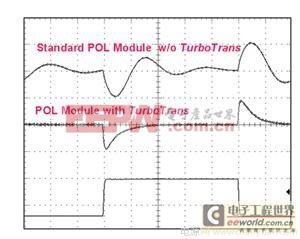

许多设计人员发现能够正常的使用所有陶瓷电容或聚合物钽质电容,因为这些电容的体积很小,而且可达到无铅焊锡的规范。在过去,使用这一些电容会引发某些POL电源模块的稳定性疑虑。使用TurboTrans后,T2模块的稳定性会实质提升,因此可达到适切控制的瞬时负载响应(见图4)。

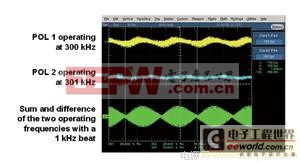

另一方面,TI的SmartSync功能也能帮助系统模块设计人员使用需要复杂电源配置设定的IC。当电源模块以不同频率运作时,这些频率的总和与差异所造成的拍差频率(beat frequency)会使EMI滤波不易达成。图5显示两个信号范例,第一个信号的频率为300kHz,第二个信号的频率为301kHz。拍差频率为1kHz。SmartSync能够让设计人员将多个T2模块的切换频率同步为特定频率,经过同步的模块可消除拍差频率,并且使EMI滤波更容易达成。

SmartSync允许将同步频率设定为高于或低于模块的一般自由运作频率。SmartSync可用来为频率范围介于240~400kHz之间的T2模块进行同步,因此能够让此设计发挥最佳化的模块效率,也可用于不让噪声敏感电路出现这类频率,以便将切换噪声保持在特定的范围之外(也就是接收器的IF频率)。可一并同步的T2模块没有数量方面的限制。

这项技术的另一项优点是减少输入电容。T2模块能够以不同的相位角度进行同步 (使用外部电路系统)。在某些应用中,这可平衡来源电流,还可以使用较小的输入电容。

相较于前几代的5%容差,TI的全新TCI6482、FPGA、ASIC及微处理器等先进DSP需要更小的3%核心电压(VCC)容差,这个容差必须包含由于静态(DC)与动态(AC)等操作条件变更而造成的所有输出电压偏差。为符合这项规格,T2电源模块的设计一定要达到更小的1.5% DC容差,做法包括设定点精确性、负载/线路调节、温度变化与长时间漂移。

如果DC容差为1.5%,则由于瞬时负载造成的AC偏差必须小于1.5%。全新的T2电源模块结合相当严格的DC调节与TurboTrans技术,可便于将任何运作条件下的输出电压维持在3%的容差内。所有T2电源模块都含有差动遥感(differential remote sense),可协助在负载时维持这个高度精确性。